C2R Gate

C2RTL技術をベースとした高位合成ツールC2R Gateの販売とサポート

C2RTL技術をベースとした開発環境と技術的サポートをご提供します。また、お客様のハードウェアIP開発支援も展開しています。

C2R Gateについて

C2R Gateは、C2RTL技術をベースにした高位合成ツールです。高位合成だけにとどまらず、IP(プロセッサ、バス、アクセラレータ、IO等)ライブラリにより、ASIP開発ツールとしての機能も充実しています。

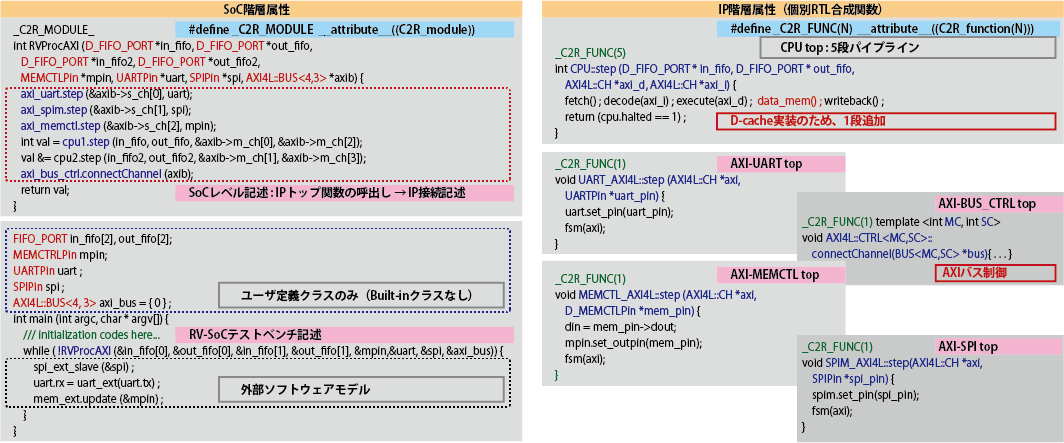

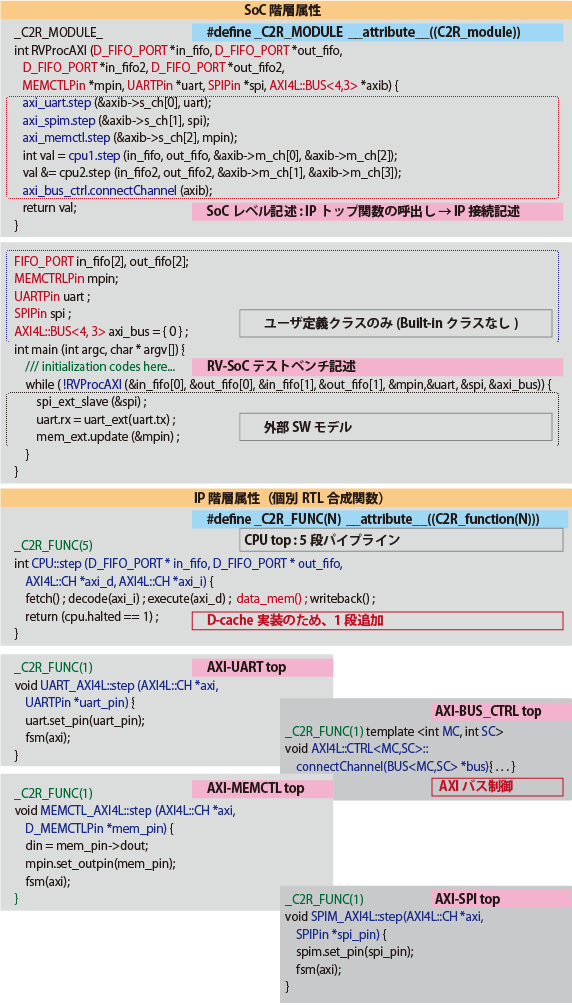

SoCを構成する全てのIP部品と、SoCインテグレーション(各IPの接続等)を全て同一ソフトウェア言語(C͏/͏C++)で設計できます。

高速システム検証モデル(動作レベル・サイクルレベル)とRTL回路モデルを同時に出力可能になり、SoC開発効率を飛躍的に向上します。

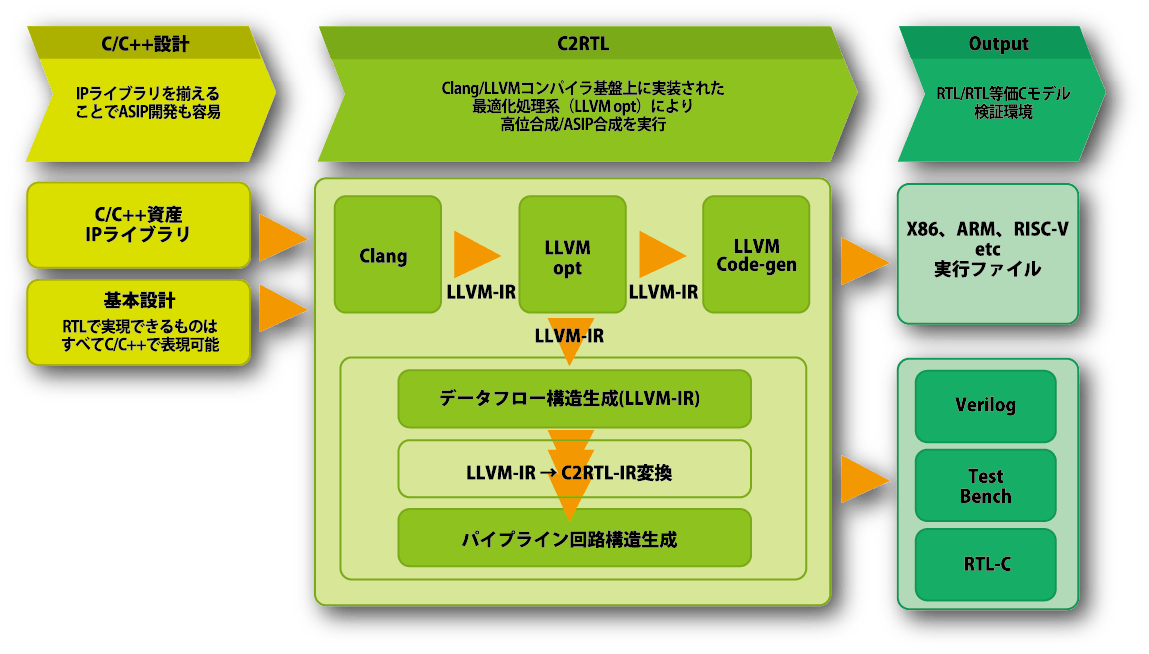

C2RTL技術とは

C2RTL技術は、C͏/͏C++記述ベースのRTL(Register-Transfer Level)設計フレームワークです。

LLVMコンパイラ基盤を利用しLLVM中間言語(LLVM-IR)を入力とした最適化処理系(LLVM optimizer:opt)エンジンとして、LLVMコンバイラ基盤上に実装されています。

任意のハードウェア回路構造をソフトウェア記述(C͏/͏C++言語)によって直接表現できます。

ソフトウェア記述そのものがRTL構造を表現する点が特徴です。

特徴1

システム設計の「見える化」が可能

・ソフトウェア記述(C͏/͏C++)でシステム全体の動作検証モデル・論理合成モデルを統一的に表現

・高い抽象度で全システムを見通すことが可能

・ソフトウェア記述によるハードウェアIP開発の容易化

・ソフトウェア記述によるシステム検証が可能

特徴2

C͏/͏C++記述によるRTL構造表現(データパス、FSM、サブシステム)が可能

・データフローC͏/͏C++記述(1サイクル記述)

・C͏/͏C++準拠(既存C͏/͏C++開発環境利用可)

・ハードウェア属性記述(pragma/CGG-attribute)にてBit幅/レジスタ/メモリを表現

統合化された設計環境を提供

・RTL等価Cモデルを自動生成することで元のC͏/͏C++開発環境でRTL検証可能

・RTL検証環境の自動生成することで検証時間を短縮

特徴3

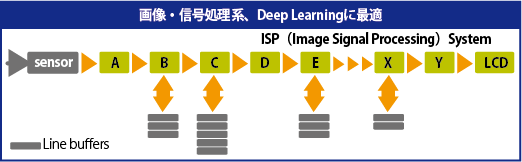

アプリケーションに合わせたC͏/͏C++データフロー記述が可能

<データフロー型単純パイプライン記述>

・高並列/パイプライン処理

・パイプラインストール制御なし

・パイプライン段数調整/論理遅延平滑化

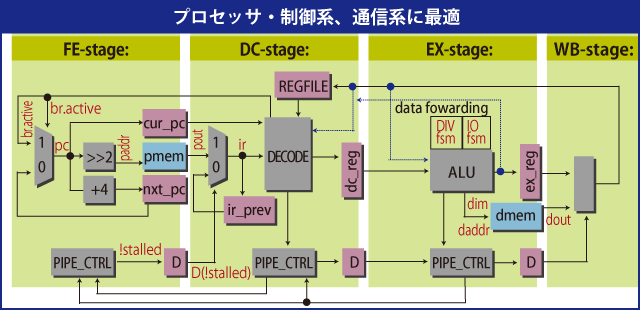

<フロー制御付きパイプライン記述>

・複雑なフロー制御を「逆方向参照」で詳細記述

・プロセッサCモデルで必須(ストール制御、data forwarding)

・詳細なパイプライン構造をC͏/͏C++データフロー記述で表現可能

特徴4

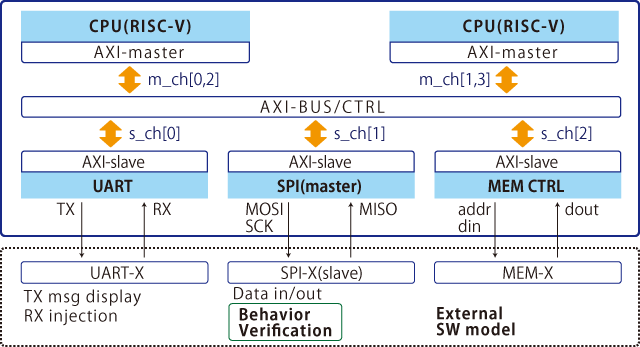

ASIP開発ツール機能

・IPライブラリを準備することで、ASIP開発ツールとして使用可能

例)RISC-Vプロセッサ開発例

IPライブラリ

RISC-Vx2:キャッシュ付き、AXI-Master x2/コア

UART:AXI-Slave

SPI:AXI-Slave

MEMCTRL:AXI-Slave

AXI-BUS:4-Master,3-Slave

動作環境マシンスペック OS:Windows10 メモリ:8Gbyte以上 CPU:Core i5

ソフトウェア環境MinGW-w64、GnuWin32、icarus Verilog